- 3 input and gate transistor diagram with vcc how to#

- 3 input and gate transistor diagram with vcc series#

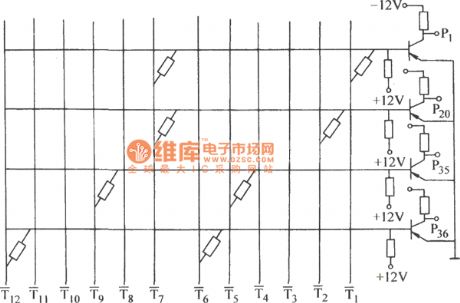

All the current is again blocked by the transistor and we get low voltage at the output, which turns OFF the LED.įig. Using PNP is quite easier: if one of their base is at 0V, that provides a path to ground with as low as 0.4 volt (in saturation, probably 0. The base to emitter junction and base to collector junction of both the transistors have a voltage lower than the threshold voltage and again they reach their cutoff state. The output of this circuit is logic 1 when either one input is logic. As the second transistor is still in its cutoff state, the emitter of the first transistor is disconnected. In next case when we press switch 1 then the base of the first transistor gets a positive value of voltage but its emitter is connected to another transistor collector. Hence at the output, we get a low voltage which turns off the LED. So, all three have to be off (their base at a. Figure 3-14 Switch model for CMOS 2-input NAND gate: (a) both inputs LOW. Since all the current coming from the collector through resistor R3 blocks by the transistor. Using PNP is quite easier: if one of their base is at 0V, that provides a path to ground with as low as 0.4 volt (in saturation, probably 0.8 in active mode), between the rail at the top and the rail at the bottom, which is NOT ENOUGH to light up the LED (1.6 V is generally required for a red one). Figure 1: Black-box representation of a 3-input, 1-output logic circuit. Draw the circuit diagram with inputs Vx1, Vx2, and Vx3 and output V f.

3 input and gate transistor diagram with vcc how to#

Therefore, the transistors act like an open switch. Show how to implement a 3-input OR gate with NMOS transistors. The NTE7410 contains three independent 3-Input NAND gates in a 14-Lead plastic DIP type package. The base to emitter junction and base to collector junction of both the transistors have a voltage lower than 0.65V, which is the practical threshold voltage of the diode.īoth junctions are in reverse bias hence both the transistors turn off and go into their cutoff state. Initially, both the switches are in OFF state so none of the transistor bases get a power supply. In a perfect world, all logic circuit signals would exist at these. a logic gate, we omit the VCC/VSS inputs and rely on the input/output logic. The base of both the transistors act like inputs and one of the emitter of either of the transistors is used to derive the output. Logic gate circuits are designed to input and output only two types of signals. A logic gate is a digital circuit that performs a logical operation on one.

3 input and gate transistor diagram with vcc series#

The transistors are connected in series and their bases are used as input.

0 kommentar(er)

0 kommentar(er)